# Lecture5

#### **Memories**

Peter Cheung Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/E2\_CAS/ E-mail: p.cheung@imperial.ac.uk

### **Lecture Objectives**

- Explain the sequence of events in reading from and writing to a static RAM

- Explain the structure and input/output signals of a static RAM

- How to design an address decoder

- Investigate the timing diagrams for a microprocessor when reading from or writing to memory

- Explain how the embedded memory in an FPGA can be used to implement memory blocks in a digital design

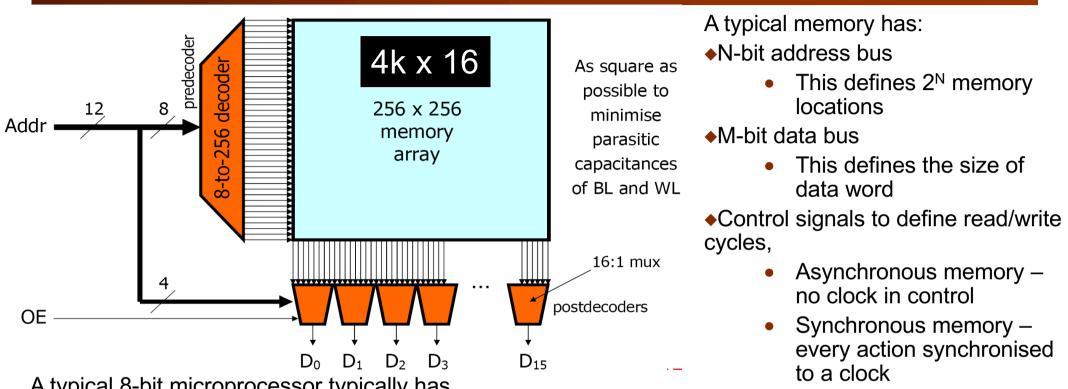

### **Simplified RAM Organization**

A typical 8-bit microprocessor typically has

- A 16-bit address bus, A15:0

- Can have up to 2<sup>16</sup>=65536 memory locations

- An 8-bit data bus, D7:0 Each data word in memory has  $2^8 = 256$  possible values

- In the RAM shown above uses 12-bit address and 16-bit data, i.e. 4096 locations of 16-bits each

- These are arranged as 256 x 256 rows of memory cells. 4096 = 256 rows x 16 columns as shown

- The address bus is therefore split into two components: 8-bit to specify which row, and 4-bit to select the correct column.

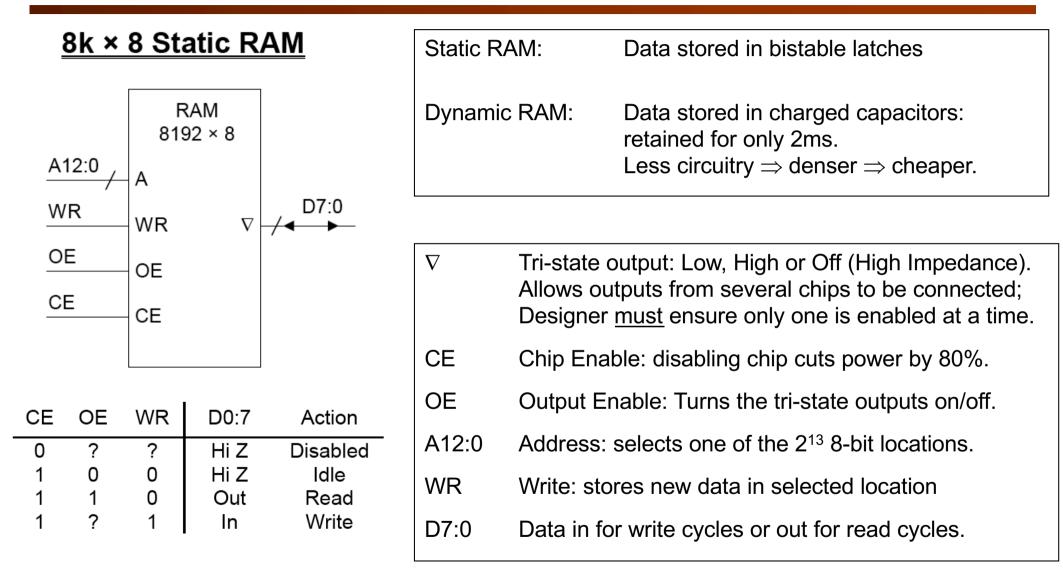

## **RAM: Read/Write Memory**

Hi Z = High impedance

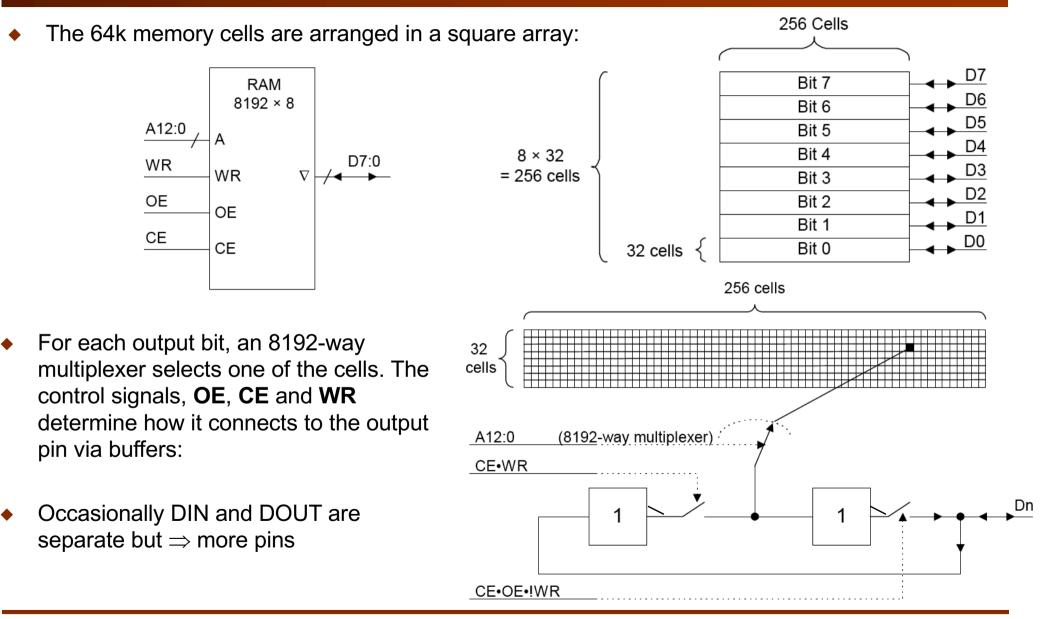

#### 8k x 8 Static RAM

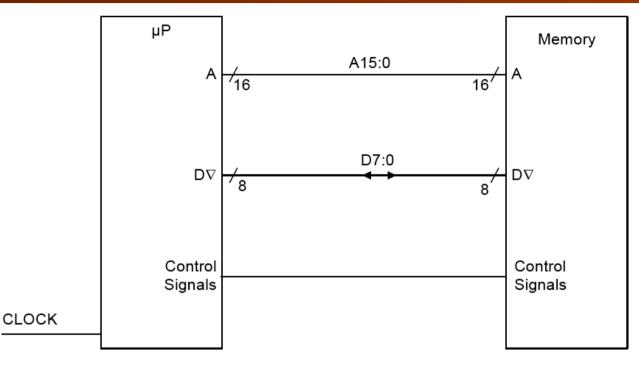

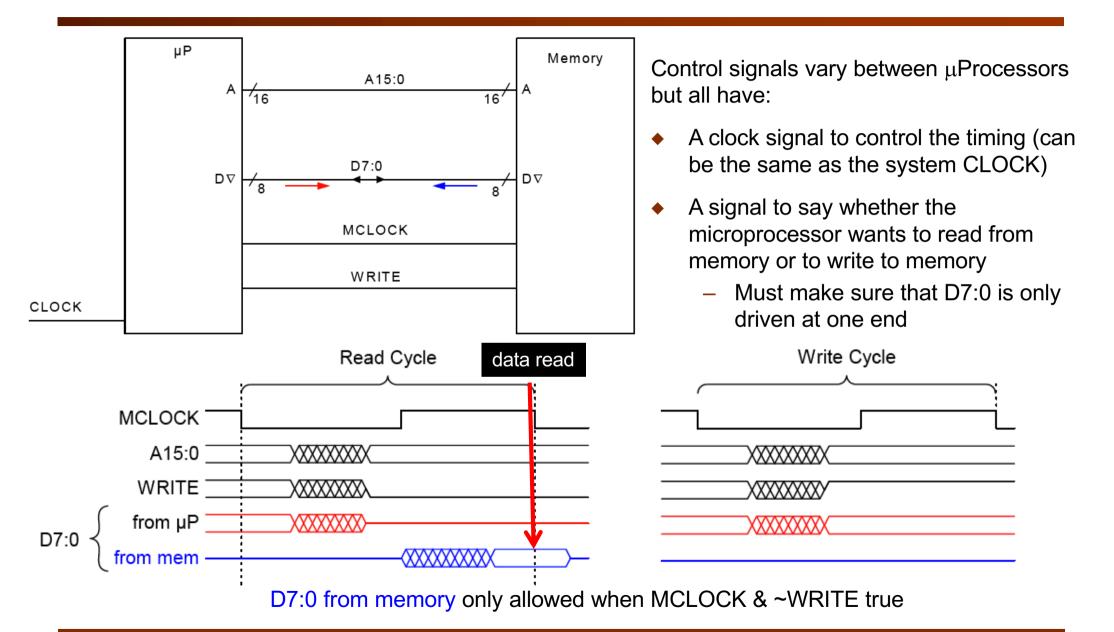

### Microprocessor 🔶 Memory Interface

- During each memory cycle:

- A15:0 selects one of 2<sup>16</sup> possible memory locations

- D7:0 transfer one word (8 bits) of information either to the memory (write) or to the microprocessor (read).

- D7:0 connections to the microprocessor are tri-state ( $\nabla$ ): they can be:

- "logic 0", "logic 1" or "high impedance" (inputs)

- The control signals tell the memory what to do and when to do it.

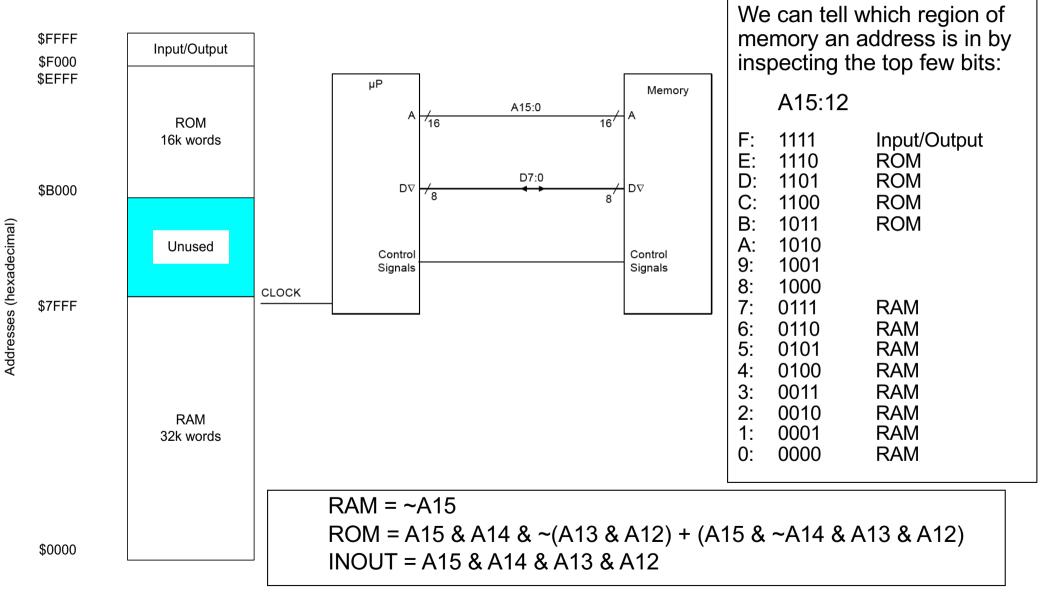

#### **Microprocessor Memory Map**

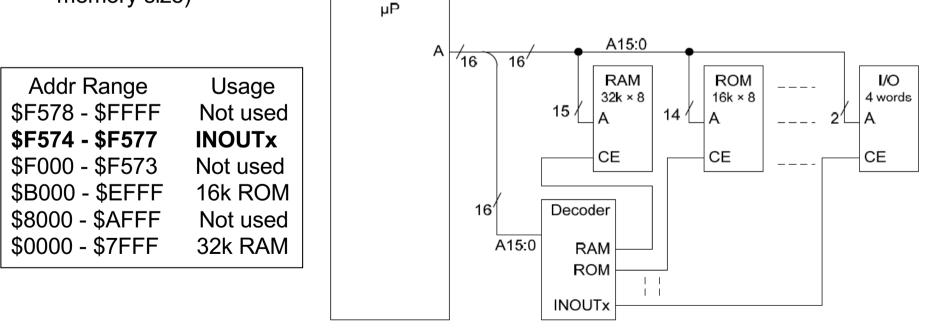

### **Memory Chip Selection**

- Each memory circuit has a "chip enable" input (CE)

- The "Decoder" uses the top few address bits to decide which memory circuit should be enabled.

Each one is enabled only for the correct address range:

RAM =  $\sim$ A15 ROM = A15 & A14 &  $\sim$ (A13 & A12) + (A15 &  $\sim$ A14 & A13 & A12)

```

INOUTx = A15 & A14 & A13 & A12 & ~A11 & A10 & ~A9 & A8 & ~A7 & A6 & A5 & A4 & ~A3 & A2

```

- INOUTx responds to addresses: \$F574 to \$F577 other I/O circuits will have different addresses

- Low *n* address bits select one of 2<sup>n</sup> locations within each memory circuit (value of n depends on memory size)

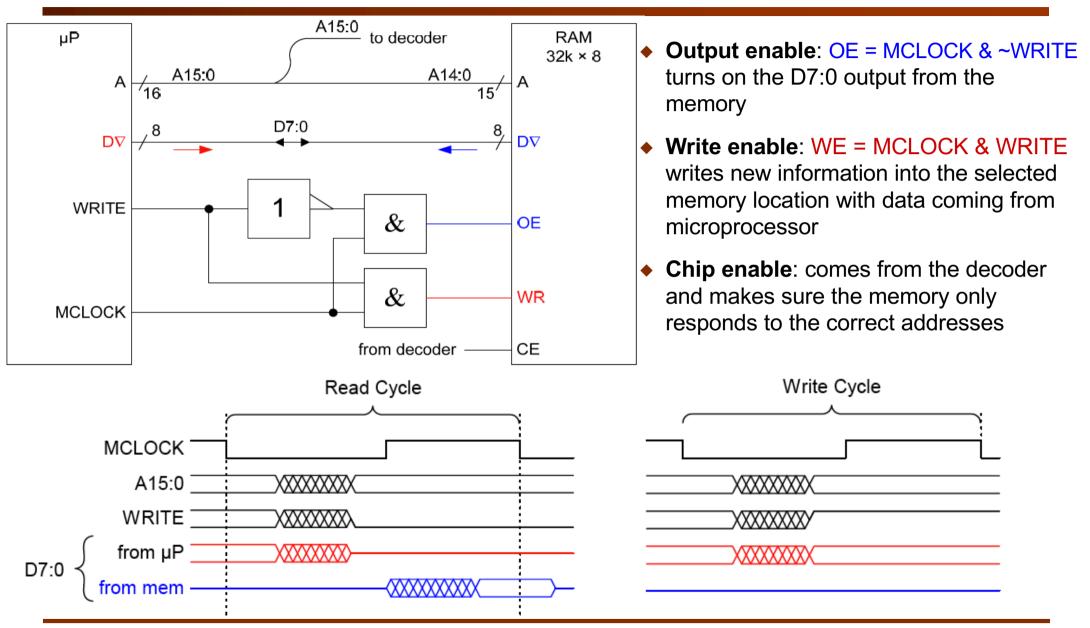

### **Memory Interface Control Signals**

### **Memory Circuit Control Signals**

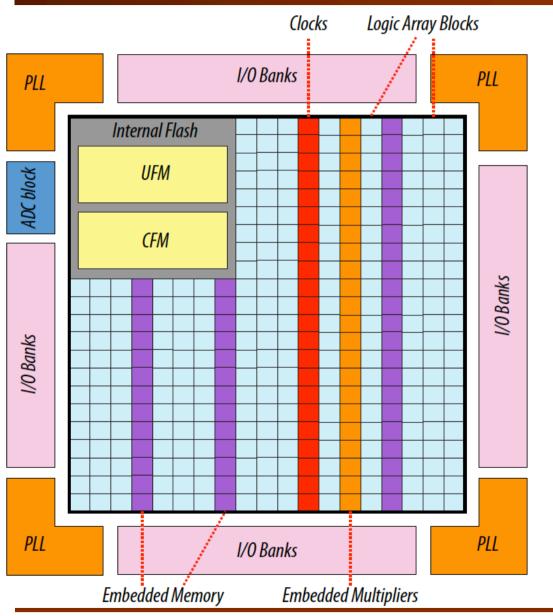

#### Max 10 FPGA – Embedded blocks

- MAX10 device: 10M50DAF484C7G

- 50,000 Logic Elements (4-LUT + FF)

- 182 M9K embedded memory blocks

- ✤ 5,888 kbits user flash memory

- 144 hard multiplier (18 x 18)

- ✤ 4 PLL (for clock generation

#### **MAX 10 Embedded Memory**

- Each 9kbit memory block (M9K) can be configured with different data width from 1 bit to 36 bit wide

- It also has multiple operating modes (which is user configurable), of which we will focus on the following only: 1-port ROM, FIFO, 2-port RAM

- Single-port

- Simple dual-port

- True dual-port

- Shift-register

FIFO

$Depth \times width$

Configuration

| 4096 × 2        |

|-----------------|

| 2048 × 4        |

| $1024 \times 8$ |

| $1024 \times 9$ |

| $512 \times 16$ |

| $512 \times 18$ |

| $256 \times 32$ |

| $256 \times 36$ |

M9K Block

$8192 \times 1$

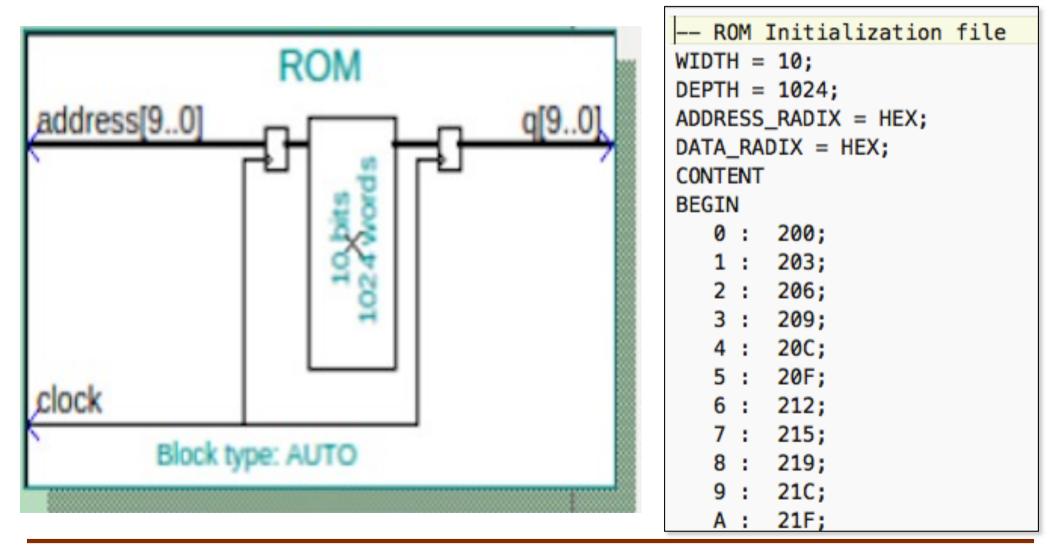

# Intialization of ROM Contents (1k x 8)

• Create ROM and initialize its content in a .mif file:

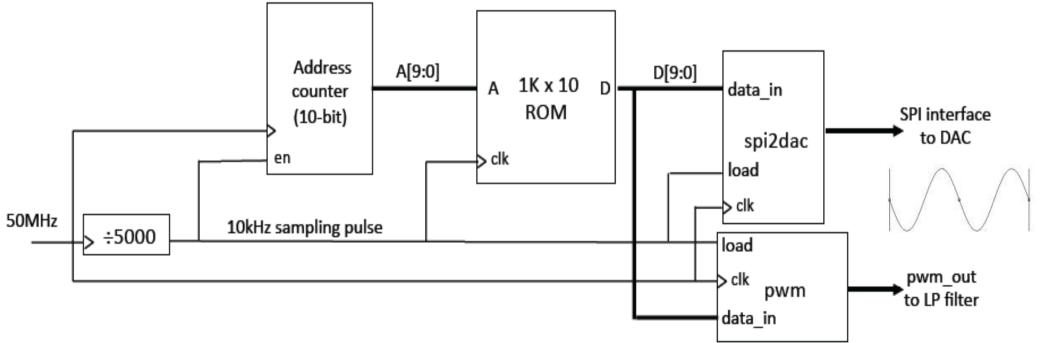

### **Sinewave Generation**

- Generate any waveform or function y = F(x) using table lookup

- Phase counter increment phase whenever step goes high

- ROM stores one cycle of sinewave to produce F(x)

- Digital-to-Analogue convert and the PWM DAC generate the analogue outputs on L & R channels

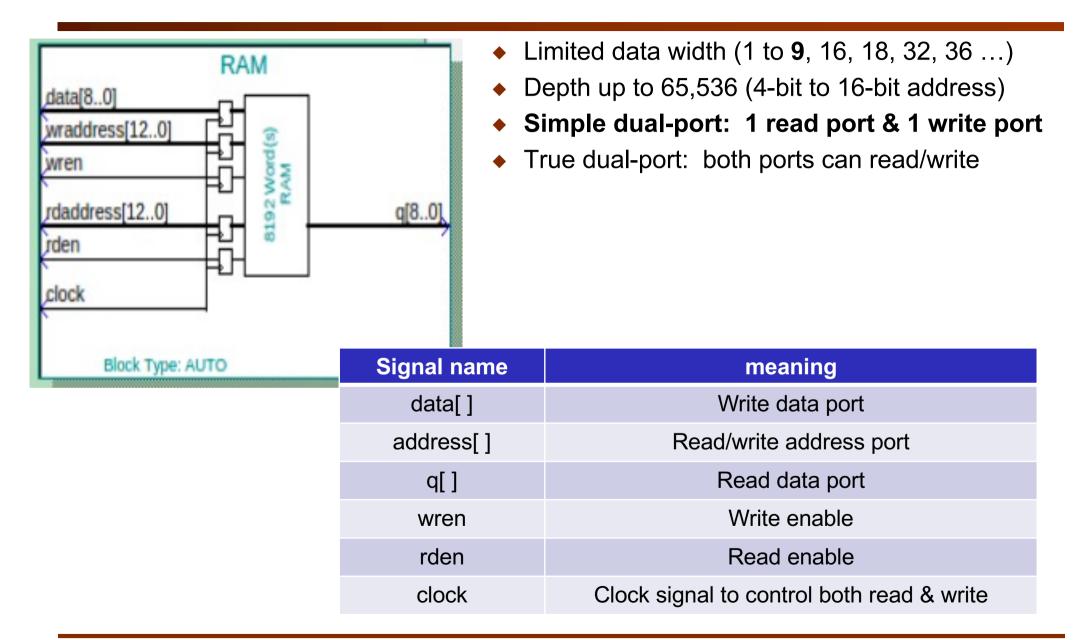

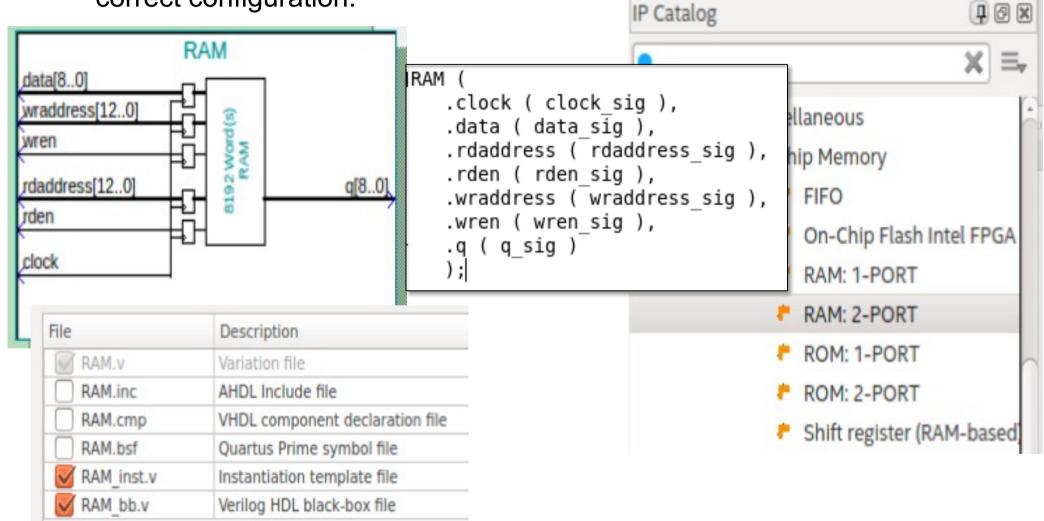

### Dual-port RAM (8k x 9)

# How to use M9K memory block? (8k x 9)

Use IP Catalog manager tool in Quartus to produce memory of the correct configuration:

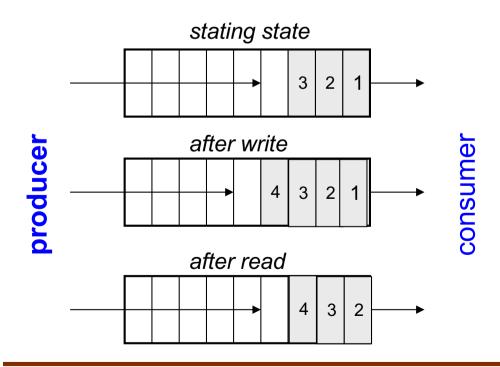

# **First-in-first-out (FIFO) Memory**

- Used to implement queues.

- These find common use in computers and communication circuits.

- Generally, used for rate matching data producer and consumer:

- Producer can perform many writes without consumer performing any reads (or vice versa). However, because of finite buffer size, on average, need equal number of reads and writes.

- Typical uses:

- interfacing I/O devices. Example network interface. Data bursts from network, then processor bursts to memory buffer (or reads one word at a time from interface). Operations not synchronized.

- Example: Audio output. Processor produces output samples in bursts (during process swap-in time). Audio DAC clocks it out at constant sample rate.

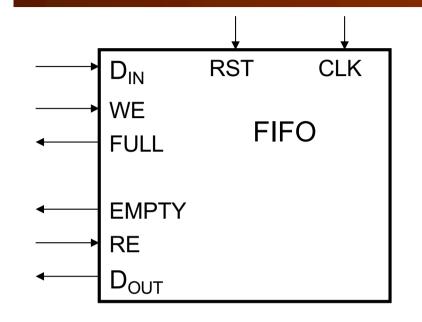

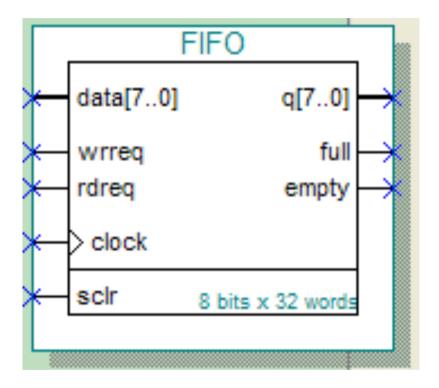

## **FIFO Interfaces**

- After write or read operation, FULL and EMPTY indicate status of buffer.

- Used by external logic to control own reading from or writing to the buffer.

- FIFO resets to EMPTY state.

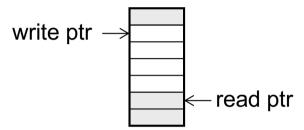

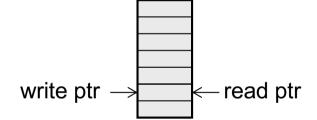

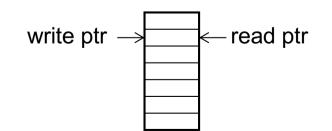

Address pointers are used internally to keep next write position and next read position into a dual-port memory.

If pointers equal after write  $\Rightarrow$  FULL:

If pointers equal after read  $\Rightarrow$  EMPTY:

#### M9K Memory as FIFO (8-bit x 32 word)

module FIFO ( clock, data, rdreg, sclr, wrreg, empty, full, q); input clock; [7:0] data; input input rdreg; sclr; input input wrreg; output empty; output full; output [7:0] q;

endmodule